Air Force considers new custom ASIC to handle wideband RF phased array beamforming

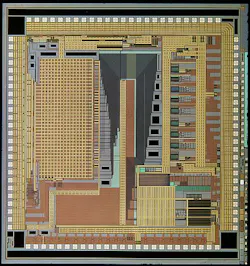

WRIGHT-PATTERSON AFB, Ohio, 11 June 2013. U.S. Air Force researchers are reaching out to industry to find companies with the technical expertise to design a custom application-specific integrated circuit (ASIC) able to function as a powerful digital phased array RF beamformer.

Scientists at the Air Force Research Laboratory at Wright-Patterson Air Force Base, Ohio, have released a request for information (RFI-RQKS-2013-0001) for the Wideband Phased Array ASIC program, which is looking into the feasibility of using an ASIC for a wideband element level digital phased array beamformer.

This RF digital beamforming device would operate on frequencies from 2 to 18 GHz, and could support eight simultaneous users on receive and transmit. the ASIC would generate pulse descriptor words (PDW), provide high-speed data interfaces, generate arbitrary waveforms, and perform element level beamforming while supporting eight users simultaneously across 64 channels.

The current implementation takes the 16x64 radiating elements and passively combines each column to form a channelized system that is digitized using commercial off the shelf (COTS) data converters and field programmable gate arrays (FPGAs).

The FPGAs provide the system with channel-to-channel calibration, phase coherency, and generation of pulse descriptor words (PDWs). The digital processing back end dissipates about 800 Watts and requires a rack-mount chassis to house the units.

Air Force scientists are interested in a new custom ASIC to handle the increased data requirements of element level digital beamforming to make the most of the generated element level and column level data prior to system level data stitching.

Methods used today passively combine each column of the 16x64 radiating elements to form a channelized system digitized with commercial off the shelf (COTS) data converters and field programmable gate arrays (FPGAs), researchers say.

The FPGAs provide the system with channel-to-channel calibration, phase coherency, and generate pulse descriptor words (PDWs). The digital processing back end dissipates about 800 Watts of power and requires a rack-mount chassis.

The requested ASIC would provide element level weighted coefficients per user request while maintaining phase coherency. A high frequency clock will be provided at each node and an aggregator chip will be provided prior to interfacing with the end user.

Researchers say they do not expect to the phased array antenna, phased array system power management, heat dissipation and cooling, passive combining, receiver, transmitter, or data converters for this project.

Key considerations should include common considerations between receive and transmit; antenna Array spacing of 0.5 inches; nodes organized in a master slave configuration; high speed low-voltage differential signaling of more than 10 gigasamples per second; ability to track and receive six signals of interest per eight users; and channel-to-channel co-calibration for gain and phase.

Companies interested should respond with white papers no later than 30 June 2013. Email white papers to the Air Force's Pompei Orlando at [email protected].

For questions or concerns contact the Air Force's Jo Ann Sillaman by emailat [email protected], or by phone at 937-255-5380.

More information is online at https://www.fbo.gov/spg/USAF/AFMC/AFRLWRS/RFI-RQKS-2013-0001/listing.html.