DARPA RF-FPGA program awards six contracts to develop programmable RF front-ends

ARLINGTON, Va., 30 Aug. 2012.RF and microwave technology experts at the U.S. Defense Advanced Research Projects Agency (DARPA) in Arlington, Va., are working with six defense companies and universities to develop programmable RF front-end components to reduce costs and development time for military communications, electronic warfare (EW), and signals intelligence (SIGINT) systems.

DARPA has awarded six contracts thus far for the Radio Frequency Field Programmable Gate Arrays (RF-FPGA) program, which seeks to reuse the same set of RF front-end components across different applications by programming the transceiver chain.

Essentially, the DARPA RF-FPGA program attempts to do for RF and microwave technology what field-programmable gate arrays (FPGAs) have done for digital computing, which is to reduce costs, cut development time, and ease development across a broad range of applications.

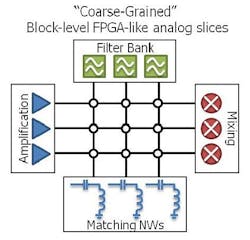

The RF-FPGA program will develop technology that eliminates redundant and costly hardware development necessary to use a new wireless function or waveform. RF FPGA components will contain analog circuitry with reprogrammable functions. Unlike digital FPGAs, however, the program does not seek to develop technology that strictly uses typical gate-level digital FPGA hardware.

Those DARPA has chosen to participate in the RF-FPGA program are the Northrop Grumman Corp. Electronic Systems segment in Linthicum, Md.; the University of Southern California (USC) in Los Angeles; the Boeing Co. Research & Technology segment (BR&T) in Seattle; Colorado Engineering Inc. in Colorado Springs, Colo.; the IBM Thomas J. Watson Research Center in Yorktown Heights, N.Y.; and Purdue University in West Lafayette, Ind.

Northrop Grumman won a $9.5 million contract on 17 Aug.; USC won a $3.3 on 20 Aug.; Boeing won a $2 million contract on 15 Aug.; Colorado Engineering won a $1.9 million contract on 6 Aug.; IBM won a $1.2 million contract on 30 July; and Purdue won a $861,049 contract on 6 July.

DARPA researchers say the hardware its contractors develop in the RF-FPGA program will help realize dynamically programmable analog and RF blocks and programmable transceivers capable of configuring for a variety of wireless applications while maintaining near optimal performance. The RF-FPGA program hardware also should be adaptable to future wireless standards.

Ultimately, the program seeks to reduce costly and time-consuming application-specific integrated circuit (ASIC) tape-outs by capturing the performance of several RF systems in one RF-FPGA design cycle, DARPA officials say.

For more information contact Northrop Grumman Electronic Systems online at www.es.northropgrumman.com; USC at www.usc.edu; Boeing Research & Technology at www.boeing.com; Colorado Engineering at www.coloradoengineeringinc.com; the IBM Thomas J. Watson Research Center at www.watson.ibm.com; or Purdue University at www.purdue.edu.

Additional information about the DARPA RF-FPGA program is online at https://www.fbo.gov/index?s=opportunity&mode=form&id=7c438631d57659b7b9f932df6d3da484&tab=core&_cview=1.

Follow Military & Aerospace Electronics and Avionics Intelligence news updates on Twitter

John Keller | Editor

John Keller is editor-in-chief of Military & Aerospace Electronics magazine, which provides extensive coverage and analysis of enabling electronic and optoelectronic technologies in military, space, and commercial aviation applications. A member of the Military & Aerospace Electronics staff since the magazine's founding in 1989, Mr. Keller took over as chief editor in 1995.