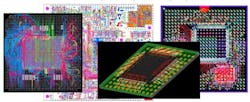

Mentor Graphics Xpedition Path Finder Suite designed for IC/package/PCB design optimization, assembly, and visualization

WILSONVILLE, Ore., 11 June 2014. Mentor Graphics Corp.’s (NASDAQ:MENT) Xpedition Path Finder product suite enables designers to assemble and optimize complex electronic systems, which can lend to improved designs, increased chip performance, and cost efficiency.

This latest addition to the Mentor Graphics Xpedition platform leverages layout data from the IC and board design teams to guide and automate IC package selection and optimization.

The Xpedition Path Finder suite provides a single environment for cross-domain design teams to model every device/interface to the level of detail and accuracy they require, officials say. IC layout design data can be represented as a virtual die model (VDM), containing all of the IC-level detail specific to the co-design and optimization process. Board design data can be modelled as individual interfaces or as complete designs. Packages can be built based on pin array generation and manipulation capabilities, existing devices, and industry-standard formats. Cross-domain design teams can make smart planning and optimization decisions related to cost and performance of their IC package in context of the complete system.

“Mentor’s Xpedition Path Finder technology provides unique capabilities not found elsewhere, which is important for our business as a design services partner for major semiconductor companies,” said Farhang Yazdani, president and chief technical officer of BroadPak. “We’re realizing substantial time and cost savings using Path Finder, while improving the overall quality and performance of the package designs.”

Addressing the increasing design complexity of system on chip (SoCs) and multi-die packaging growth, the suite provides new path-finding methodology that automates the planning, optimization, and connectivity from a chip through multiple packaging variables, while targeting multiple and different PCB platforms.

Using the multi-mode connectivity environment, designers can capture and manage connectivity based on their preference: table-based, graphical schematics, or automated. Cross-domain pin mapping and net combining can easily be managed in all modes of connectivity capture. In addition, users can perform rules-based pin/ball-out studies from their respective domains, by signal, bus or interface, visualizing the impact across the complete system in real time. Path Finder also streamlines and automates the library development process.

“The exponential increase in electrical systems design complexity is motivating Mentor to deliver solutions to the marketplace that address new design and manufacturing challenges,” explains Henry Potts, general manager and senior vice president of Mentor Graphics Systems Design Division. “We are very excited by the customer feedback we have received on our Path Finder technology and we are looking forward to wider deployment, enabling designers to achieve optimum productivity.”

The Xpedition Path Finder suite includes a multi-mode connectivity engine and optimization engine/editor, leveraging a physical layout tool with industry-leading routing technology. Additional features in the Path Finder suite include:

• A correct-by-construction layout environment that enables designers to optimize performance and manufacturability on the densest designs populated by high-pin-count flip-chip BGAs. The core Xpedition layout tool provides: unique BGA breakout and escape algorithms coupled with support for complex microvia structures; shape-based, any-angle routing; plane areas that dynamically fill around traces and vias during editing; patented technology enabling efficient, concurrent design by large teams; and integrated RF circuit design and optimization

• Rule-based ball-out assignment, including an optimization engine/editor for planning by bank, byte, reference voltage, clock domain, etc. – an intelligent way to show a ball map: simply create, import, and export

• Single tool for multi-mode physical design (PCB, MCM, SiP, RF, Hybrid and BGA designs) that reduces design time orders of magnitude compared to other available products – using Microsoft-based Component Object Model (COM) automation for robust extension and customization capabilities

• Streamlined and fully automated library development

• Virtual Die Model (VDM) to accurately capture IC layout (floor planning) design intent, facilitating WYSIWYG IC and package co-optimization.

• Tight integration with 2D and 3D electro-magnetic (EM) and computational fluid dynamics (CFD) thermal analysis engines

The Xpedition Path Finder suite, available today and an EDA vendor-neutral flow, leverages other Mentor Graphics tools such as the HyperLynx signal and power integrity product, and 3D full-wave EM analysis tools, Xpedition layout technology, the FloTHERM CFD thermal modelling tool, visECAD/CAMCAD design comparison tool, and Valor NPI substrate fabrication checking tool.