By Ross Bannatyne, VORAGO Technologies and Eoin McCann, ARM

On 19 February 2017, the SpaceX CRS-10 cargo resupply mission to the International Space Station (ISS) blasted off on a Falcon 9 rocket from Cape Canaveral Air Force Station in Florida. Inside is an important piece of experimental electronics that could change the way we design radiation-hardened (rad-hard) systems, powered by ARM and Vorago Technologies.

Part of payload in the Dragon space capsule is a module known as the Radiation Hardened Electronic Memory Experiment (RHEME) that was developed by the Air Force Research Laboratory (AFRL) and built by the COSMIAC Research Center at the University of New Mexico. RHEME is an important science study, sponsored by AFRL and hosted on the STP-H5 experiment payload by the Air Force Space and Missile System Center Space Test Payload (AF SMC/STP) group and NASA.

The International Space Station is located at an orbit height of 249 miles in Low Earth Orbit (LEO) and travels around the earth at 17,200 miles per hour, completing an orbit every 92.6 minutes. It is an ideal platform for material science experiments. The devices under test have already been subjected to radiation testing at several gamma-ray and cyclotron facilities on earth, but there is no substitute for the three-dimensional (3D) and combined effects of space. What researchers find in the coming months may change the way we design against the effects of radiation in electronics and accelerate innovation in space exploration.

Studying the effect of particle strikes on CMOS memory

The purpose of RHEME is to study the frequency and effect of high-energy particle strikes on CMOS (complementary metal oxide semiconductor) memory devices in space. There are nine specially processed die used in the experiment, which will be conducted over the duration of one year. Four 16Mb SRAMs and a 72Mb SRAM stack (composed of four 18Mb devices) are used as targets for space radiation and this array is monitored and controlled by a VORAGO Technologies ARM Cortex-M0 based microcontroller. All the specially processed die use the HARDSIL process, developed by VORAGO. The system is shown in Figure 1.

Figure 1 – RHEME system (Photo courtesy of COSMIAC)

VORAGO’s chips are subject to extensive radiation hardening for maximum resilience

HARDSIL is a technology that was developed to harden bulk CMOS semiconductors against the effects of radiation. Any CMOS device at any geometry, produced in any fab, can be modified by HARDSIL to immunize the device against latch-up. Depending on the specific process, it will add one to two mask layers and two to three implants on the wafer. The result is immunization against latch-up, the most serious effect of space radiation on CMOS devices.

All bulk CMOS semiconductors contain millions of parasitic transistor structures that are an artifact of the CMOS device architecture and processing steps. In most cases, as long as the device is operated within specification, the parasitic structure that resembles and behaves like a thyristor is not problematic. An ionizing particle strike can create a charge build up on the substrate that can forward bias the parasitics and switch-on the structure. This will create a short circuit between Vdd and Vss that will inhibit the operation of the device. If latch-up is detected early enough, the device can sometimes be reset to get out of the latch-up condition, otherwise it can destroy the chip.

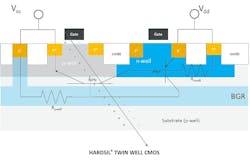

HARDSIL works by implementing a Buried Guard Ring (BGR) below the CMOS devices to create a low impedance path for unwanted charge and reduce the gain of the NPN transistor in the parasitic structure. A CMOS structure with the parasitics and BGR is shown in Figure 2. When the combined gain of the parasitic NPN and PNP is <1, latch-up cannot be sustained.

Figure 2 – HARDSIL BGR Implementation

Using devices that are latch-up immune is a key characteristic of the RHEME project, since it is now possible to observe the effect of space radiation on the memory arrays without concern about them or the Cortex-M0 controller latching-up.

Space radiation particles can corrupt memory

When a space radiation particle strikes a memory cell, the ionizing effect can create a charge on the silicon that can flip the memory bit. Figure 3 illustrates the passage of a particle through a silicon wafer depicting the charges that are created on the device. This is a problem as it can corrupt data or program memory. The devices that are used in the RHEME experiment (including the Cortex-M0, that also has on-chip memory) all include an Error Detection and Correction (EDAC) subsystem that detect when a memory bit has flipped and can correct it. It is thus possible to observe the effect of particle strikes on the memory while correcting them on an ongoing basis, so that the experiment can be continued for the duration of the mission. This is important data as the actual results that are observed over a year in Low Earth Orbit can be compared to the radiation testing and modelling data that was performed in the lab on Earth. This allows the Earth-based radiation testing and modelling to be improved to more closely resemble actual space conditions. It is also interesting to note that the memory devices have several modes of operation that allow the EDAC to be turned on and off. This allow the experiment to look at multiple aspects of memory design and error correction.

Figure 3 – Effect of Ionizing Particle Strike

The EDAC operates when a word of memory is fetched by the CPU. For each byte in a 32-bit word, it is possible to detect two flipped bits and correct one. Additional precautions are taken to reduce the likelihood of two flipped bits within a single byte. One such precaution is laying out the physical memory so that logically adjacent bits are not located physically adjacent. Another precaution is the implementation of a Scrub engine. The Scrub engine operates autonomously of the CPU to sequentially step through memory locations testing for flipped bits and correcting them. This is a powerful defense against uncorrectable errors as it helps to ensure that the memory is clean even before the EDAC fetches a word. The speed of the Scrub engine can be adjusted in real time to compensate for different solar radiation conditions that may occur.

The combination of latch-up immunity and the ability to observe and correct memory upsets represents an ideal set of hardware to implement the RHEME experiment.

A VORAGO ARM Cortex-M0 based microcontroller is used at the heart of the system to control and observe the memory devices. The microcontroller is also latch-up immune and has the same extensive memory protection system with EDAC and Scrub engine implemented. All the registers are protected from Single Event Upsets (SEUs) and Single Event Functional Interrupts (SEFIs) by the implementation of Triple Modular Redundancy in the form of DICE latches. Each latch consists of three voting elements to ensure that a particle strike will not disrupt the logic functions.

A standardized architecture for space applications

There has been a very favorable response to the availability of radiation-hardened ARM Cortex-based microcontrollers for space applications. The low-power consumption characteristics are important as spacecraft rely on solar energy for power. In addition, the development support provided by the world’s number one ecosystem allows designers to choose the right solution for their specific PPA and cost requirements. These microcontrollers are increasing in popularity, particularly in small satellite platforms such as CubeSats. Small satellites often have significant space constraints, so the small footprint of the package and high level of integrated peripherals is also an attractive feature.

Further missions for the RHEME chipset on spacecraft to Geosynchronous orbit (GEO) that match the Earth’s rotation period and Low Earth Polar orbit will follow in the near future. GEO orbit is at an altitude of 22,236 miles above Earth sea level. Polar orbit is an elliptical trajectory that passes above both poles of Earth.

VORAGO microcontrollers based on the Cortex-M0 processor are proving to be popular in many applications destined for space, particularly SmallSat/CubeSat designs that usually have a challenging project budget and aggressive development schedule. ARM’s DesignStart program gives free access to the Cortex-M0 processor and a fast track to licensing, enabling even more people to develop innovative technology such as this. The availability of such chips will increase the rate of innovation that in space exploration being demanded of visionaries such as Elon Musk that dream of a day where travel to Mars is like a transatlantic flight today. Finding a way to counteract the effects of the harsh environment is critical to making that happen.