By John McHale

EL SEGUNDO, Calif. - Raytheon Space and Airborne Systems engineers have developed computer architectures able to adopt different forms depending on their application, reconfiguring and adapting to mission requirements on the fly.

The architecture brings system-on-a-chip capability to the U.S. Department of Defense (DOD) without relying heavily on commercial processors.

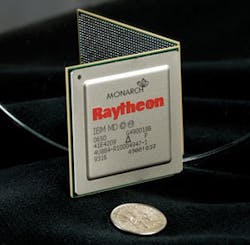

The adaptable processors called MONARCH-short for morphable networked microarchitecture-address the large data volume of sensor systems, as well as their signal and data-processing throughput requirements. It performs as one system on a chip, which reduces the number of processors necessary for computing systems, and performs in an array of chips for teraflop-level throughput.

The morphing can happen on the fly, depending on applications such as beamforming, Raytheon officials say. MONARCH can look like a PowerPC Altivec general-purpose processor, and then look like a streaming processor. Its six RISC processors can morph into different programming modes for reconfigurable data flow, RISC scalar, and RISC SIMD (Altivec-like).

“Typically, a chip is optimally designed either for front-end signal processing or back-end control and data processing,” says Nick Uros, vice president for the Advanced Concepts and Technology group of Raytheon Space and Airborne Systems in El Segundo, Calif.

“The MONARCH microarchitecture is unique in its ability to reconfigure itself to optimize processing on the fly,” Uros says. “MONARCH provides exceptional compute capacity and highly flexible data bandwidth capability with beyond state-of-the-art power efficiency, and it’s fully programmable.”

In addition to the ability to adapt its architecture for a particular objective, the MONARCH computer is also power efficient.

“In laboratory testing MONARCH outperformed the Intel quad-core Xeon chip by a factor of 10,” says Michael Vahey, the principal investigator for the company’s MONARCH technology.

The MONARCH processor was developed under a U.S. Air Force Research Laboratory contract, which comes under supervision of the U.S. Defense Advanced Research Project Agency (DARPA) polymorphous computing architecture program.

The goal of the polymorphous initiative was to “institute a paradigm shift from static open loop to reactive closed-loop mission algorithms, application software, and hardware implementation.

DARPA officials say it should be able to reduce mission computing payload adaptation, optimization, and verification times from months and years, to minutes.

MONARCH’s polymorphic capability and super efficiency enable the development of DOD systems that need very small size, low power, and in some cases radiation tolerance for such purposes as global-positioning systems and airborne and space radar and video processing systems.

The technology has some inherent resistance to single-event upsets and total dose radiation, but radiation-hardening testing is ongoing, according to Raytheon officials.

The company has begun tests on prototypes of the polymorphic MONARCH processors to verify they will function as designed and to establish their maximum throughput and power efficiency. MONARCH, containing six microprocessors and a highly interconnected reconfigurable computing array, provides 64 gigaflops (floating point operations per second) with more than 60 gigabytes per second of memory bandwidth and more than 43 gigabytes per second of off-chip data bandwidth.

The MONARCH has 31 Memory Clusters: 124 dual-port memories, 256 words x 32 bits each (128 kilobytes), and 248 address generators.

Mercury Computer Systems, in Chelmsford, Mass., provided its Serial RapidIO IP core with DMA capability, DRAM (dynamic random-access memory) control IP, and component middleware for the MONARCH. Mercury’s IP addresses endpoint and switching communications applications.

Raytheon Space and Airborne Systems led an industry team with the Information Sciences Institute of the University of Southern California (USC) to create the integrated large-scale system on a chip with a suite of software development tools for programs of high value to the Department of Defense and commercial applications.

Besides USC and Mercury, major subcontractors included the Georgia Institute of Technology and IBM’s Global Engineering Solutions division.