Beyond CMOS: three industry teams aim at next generation of high-performance computing (HPC)

Officials of the Intelligence Advanced Research Projects Activity (IARPA) in Washington have awarded contracts to teams led by IBM, Raytheon-BBN and Northrop Grumman Corp. for the for the Cryogenic Computing Complexity (C3) program that seeks to push the frontiers of high-performance computing (HPC).

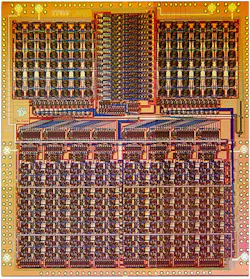

The IARPA C3 initiative seeks to establish superconducting computing as a long-term solution to the power, space, and cooling problem of traditional complementary metal-oxide-semiconductor (CMOS) designs in HPC.

Related: IARPA seeks to move high-performance computing beyond CMOS and floating point

Power and cooling demands of high-performance computers rapidly are becoming unmanageable problems, IARPA officials explain. Superconducting computing offers an attractive low-power alternative to CMOS, such that superconducting computers may be capable of 1 petaflop per second for about 25 kilowatts and 100 petaflops per second for about 200 kilowatts, including the cryogenic refrigerator.

“The power, space, and cooling requirements for current supercomputers based on CMOS technology are becoming unmanageable,” says Marc Manheimer, the C3 program manager at IARPA. “Computers based on superconducting logic integrated with new kinds of cryogenic memory will allow expansion of current computing facilities while staying within space and energy budgets, and may enable supercomputer development beyond the exascale.”

This phase of the IARPA C3 program should run through early 2017. IARPA is the research arm of the U.S. Office of the Director of National Intelligence.

In phase 1 of the C3 program, the three industry teams will try to develop the technologies necessary to demonstrate the value of superconducting computing. It has two thrusts: cryogenic memory; and logic, communications, and systems.

IBM and Northrop Grumman are working on the cryogenic memory, while Northrop Grumman and Raytheon-BBN are working on logic, communications, and systems. Also involved is the MIT Lincoln Laboratory in Cambridge, Mass., and the National Institute for Standards and Technology (NIST) in Boulder, Colo.

The cryogenic memory component seeks to create new approaches to enable high-performance computing with significantly improved memory capacity and energy efficiency compared to what is possible today. Logic, communications and systems, meanwhile, seeks to develop key superconducting logic circuits necessary to demonstrate the potential of superconducting logic for high-performance computing.

Recent technological innovations, such as new families of superconducting logic without static power dissipation and new ideas for energy efficient cryogenic memory, have created foundations for a major breakthrough in high-performance computing, IARPA officials say.

The energy demands of today’s high-performance computers have become a critical challenge for the intelligence community, IARPA officials say. During the initial phase of the C3 program, experts from the three industry teams will develop components for the memory and logic subsystems and plan the prototype computer.

Eventually experts will seek to scale and integrate the components into a working computer and test its performance using a set of standard benchmarking programs.

For more information contact IARPA online at www.iarpa.gov.