Northrop Grumman eyes quick design of defense electronics by integrating complex IP blocks

ARLINGTON, Va. – U.S. military researchers are asking Northrop Grumman Corp. to find ways of speeding how long it takes to develop new defense electronics through the reuse and integration of blocks of intellectual property (IP).

Officials of the U.S. Defense Advanced Research Projects Agency (DARPA) in Arlington, Va., announced a $7.1 million contract Tuesday to the Northrop Grumman Mission Systems segment in Linthicum, Md., for a research project under the Common Heterogeneous Integration and Intellectual Properties Reuse Strategies (CHIPS) program.

The DARPA CHIPS program seeks to establish a modular design and fabrication flow for electronic systems that can help reduce the rising cost, lead-time, and complexity of integrated circuit (IC) design.

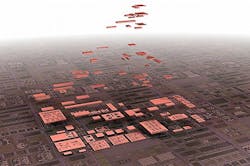

Northrop Grumman electronics experts will investigate ways to subdivide electronics into functional circuit blocks, or chiplets, that are reusable IP blocks. The idea is to create complete electronic systems by integrating chiplets, rather than fabricating circuits in a monolithic flow.

Explosive growth in mobile and telecommunication devices has pushed the semiconductor industry towards more integration of digital, analog, and mixed-signal blocks into system-on-chip (SoC) solutions, DARPA officials explain.

Advanced complementary metal oxide silicon (CMOS) has enabled this integration but also has led to a rise in design and processing costs. IP reuse is helping lower design costs, but this discipline largely is confined to digital technology.

To alleviate these challenges, DARPA researchers are trying to address reusable design in the digital and analog domains to enhance overall system flexibility and reduce design time.

Northrop Grumman experts will try to assemble and reconfigure IP blocks rapidly through standard layouts and interfaces linked to other chiplets.

DARPA researchers say they expect this common framework to expand access to a large catalog of commercial off-the-shelf (COTS) and government off-the-shelf (GOTS) IP blocks, enable reuse of existing IP blocks, and speed heterogeneous integration of blocks in other technologies.

A CHIPS modular design flow should lead to a 70 percent reduction in IC design cost and turnaround time by exploring the design tools, integration methodologies, and interface standards necessary to integrate chiplets rapidly.

Ultimately, Northrop Grumman experts should be able to demonstrate not only functional modules built using chiplets but also a set of standard interfaces for future designs that capitalize on reusable chiplets.

The DARPA CHIPS program has three core challenges, DARPA officials say: creating an IP reuse ecosystem; developing integration technologies to combine process modules using standard interfaces; and integrating IP integration tools into a technology toolbox.

Related: Boeing makes five: companies to design power and thermal management for future jet fighters

The IP reuse ecosystem should help manage IP blocks from various process modules, such as silicon, gallium arsenide, gallium nitride, indium phosphide, and silicon germanium across a design and fabrication cycle.

Integration technologies should help electronics developers combine process modules interchangeably using standard interfaces. Together, these two technical areas form a technology toolbox that will enable a rapid and customizable design flow within current process technologies.

Managing the evolution of this toolbox will identify new process technologies for investment, and then quickly integrating them into a technology toolbox, DARPA researchers say.

For more information contact Northrop Grumman Mission Systems online at www.northropgrumman.com, or DARPA at www.darpa.mil.

Learn more: search the Aerospace & Defense Buyer's Guide for companies, new products, press releases, and videos