DARPA considers ASIC-based signal processing for the toughest EW and communications problems

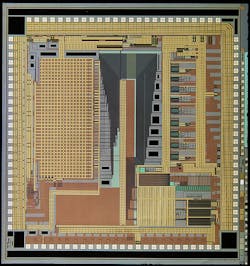

ARLINGTON, Va., 9 Feb. 2014. U.S. military researchers are considering a program to develop new kinds of digital signal processing (DSP) based on application-specific integrated circuit (ASIC) technology for advanced sensors for aircraft and space, as well as for the next generations of military communications systems and electronic warfare (EW).

Scientists at the Defense Advanced Research Projects Agency (DARPA) in Arlington, Va., are reaching out to defense companies to find out if the kinds of signal-processing technologies they envision already exist in industry or on the drawing board.

DARPA officials last week released a request for information (DARPA-SN-14-19) for the Signal Processing Co-Processor for Sensors, Communications program, which seeks to develop a co-processor that can serve a variety of military signal processing electromagnetic functions for military programs. The RFI is on behalf of the DARPA Strategic Technology Office (STO).

Advanced defense systems require a combination of programmability and throughput, DARPA officials explain. While field-programmable gate arrays (FPGAs), are programmable, they are larger, slower and much less power efficient then application specific integrated circuits (ASICs).

Related: Signal processing approaches for electronic warfare and signals intelligence spark debate

DARPA researchers are considering crafting an ASIC co-processor that can perform many kinds of signal processing functions and provide leap-ahead performance in the system's capabilities. This co-processor could be accessible by control or function calls from an FPGA or other suitable host processor.

This kind of add-on coprocessor would carry out program-specific computations with a controlled FPGA without the need to classify the co-processor. The coprocessor would be freely available to the government and its contractors without intellectual property rights limitations.

DARPA is asking for industry's advice on considerations should be given to data input/output, memory requirements, and other dedicated functions. For this project, DARPA is posing a set of questions to industry that include:

-- are there any co-processors that exist today, or that are being developed, that meet some or all of these requirements?

-- If DARPA were to develop this kind of co-processor, which types of sensor, communications, security, and EW applications would benefit?

-- Which signal processing functions should be included, and for which applications?

-- Are there libraries that should be provided with unlimited rights?

-- How large should these functions be, such as the length of its largest FFT, and what radix levels should it support?

-- What type of word size should be required, and must the co-processor be able to support variable word size?

Related: Smart Antenna technology relies on digital signal processing

-- What are the appropriate input/output formats?

-- What are the on-chip memory requirements?

-- What is the most appropriate co-processor and accelerator architecture?

-- How should the coprocessor support latency or data synchronization?

-- How does the co-processor interface with the FPGA or host processor?

-- What support tools are necessary?

Related: Radar systems combine DSP and complex A-D converters to improve range and resolution

Companies interested should email responses no later than 17 March 2014 to [email protected]. Email questions or concerns to [email protected].

More information is online at https://www.fbo.gov/spg/ODA/DARPA/CMO/DARPA-SN-14-19/listing.html.

John Keller | Editor

John Keller is editor-in-chief of Military & Aerospace Electronics magazine, which provides extensive coverage and analysis of enabling electronic and optoelectronic technologies in military, space, and commercial aviation applications. A member of the Military & Aerospace Electronics staff since the magazine's founding in 1989, Mr. Keller took over as chief editor in 1995.